Riassuntu di u wafer di SiC

Cialde di carburo di siliciu (SiC)sò diventati u sustratu di scelta per l'elettronica di alta putenza, alta frequenza è alta temperatura in i settori automobilisticu, di l'energie rinnuvevuli è aerospaziale. U nostru portafogliu copre i politipi chjave è i schemi di doping - 4H dopatu cù azotu (4H-N), semi-isolante di alta purezza (HPSI), 3C dopatu cù azotu (3C-N) è 4H/6H di tipu p (4H/6H-P) - offerti in trè gradi di qualità: PRIME (sustrati cumpletamente lucidati, di qualità di dispusitivu), DUMMY (lappati o micca lucidati per prove di prucessu) è RESEARCH (strati epi persunalizati è profili di doping per R&S). I diametri di i wafer sò di 2″, 4″, 6″, 8″ è 12″ per adattassi sia à l'arnesi legacy sia à e fabbriche avanzate. Fornemu ancu boule monocristalline è cristalli di sementi orientati precisamente per sustene a crescita di cristalli interna.

I nostri wafer 4H-N presentanu densità di purtatori da 1×10¹⁶ à 1×10¹⁹ cm⁻³ è resistività di 0,01–10 Ω·cm, furnendu una eccellente mobilità elettronica è campi di rottura sopra à 2 MV/cm, ideale per diodi Schottky, MOSFET è JFET. I substrati HPSI superanu una resistività di 1×10¹² Ω·cm cù densità di microtubi inferiori à 0,1 cm⁻², assicurendu perdite minime per i dispositivi RF è à microonde. Cubic 3C-N, dispunibule in furmati di 2″ è 4″, permette l'eteroepitassia nantu à u siliciu è supporta nuove applicazioni fotoniche è MEMS. I wafer 4H/6H-P di tipu P, drogati cù aluminiu à 1×10¹⁶–5×10¹⁸ cm⁻³, facilitanu architetture di dispositivi cumplementari.

I wafer PRIME di SiC sò sottumessi à una lucidatura chimica-meccanica à una rugosità superficiale RMS <0,2 nm, una variazione di spessore totale inferiore à 3 µm è una curvatura <10 µm. I substrati DUMMY acceleranu i testi di assemblaggio è di imballaggio, mentre chì i wafer RESEARCH presentanu spessori di epi-strati di 2-30 µm è un doping persunalizatu. Tutti i prudutti sò certificati da diffrazione di raggi X (curva di oscillazione <30 arcsec) è spettroscopia Raman, cù testi elettrici - misurazioni Hall, profilazione C-V è scansione di microtubi - chì garantiscenu a conformità JEDEC è SEMI.

E boule finu à 150 mm di diametru sò cultivate via PVT è CVD cù densità di dislocazioni inferiori à 1 × 10³ cm⁻² è un bassu numeru di micropipe. I cristalli di sementi sò tagliati à 0,1° da l'asse c per garantisce una crescita riproducibile è alte rese di taglio.

Cumbinendu parechji politipi, varianti di doping, gradi di qualità, dimensioni di wafer SiC è pruduzzione interna di boule è cristalli di semente, a nostra piattaforma di substrati SiC semplifica e catene di furnimentu è accelera u sviluppu di dispositivi per veiculi elettrici, reti intelligenti è applicazioni in ambienti difficili.

Riassuntu di u wafer di SiC

Cialde di carburo di siliciu (SiC)sò diventati u sustratu SiC di scelta per l'elettronica di alta putenza, alta frequenza è alta temperatura in i settori automobilisticu, di l'energie rinnuvevuli è aerospaziale. U nostru portafogliu copre i principali politipi è schemi di doping - 4H dopatu cù azotu (4H-N), semi-isolante di alta purezza (HPSI), 3C dopatu cù azotu (3C-N) è 4H/6H di tipu p (4H/6H-P) - offerti in trè gradi di qualità: wafer SiCPRIME (substrati cumpletamente lucidati, di qualità per dispositivi), DUMMY (lappati o micca lucidati per prove di prucessu) è RESEARCH (strati epi persunalizati è profili di doping per R&S). I diametri di e cialde di SiC sò di 2″, 4″, 6″, 8″ è 12″ per adattassi sia à l'arnesi legacy sia à e fabbriche avanzate. Fornemu ancu boule monocristalline è cristalli di sementi orientati precisamente per sustene a crescita interna di i cristalli.

I nostri wafer SiC 4H-N presentanu densità di purtatori da 1×10¹⁶ à 1×10¹⁹ cm⁻³ è resistività di 0,01–10 Ω·cm, furnendu una eccellente mobilità elettronica è campi di ripartizione sopra à 2 MV/cm, ideale per diodi Schottky, MOSFET è JFET. I substrati HPSI superanu una resistività di 1×10¹² Ω·cm cù densità di microtubi inferiori à 0,1 cm⁻², assicurendu perdite minime per i dispositivi RF è à microonde. Cubic 3C-N, dispunibule in furmati di 2″ è 4″, permette l'eteroepitassia nantu à u siliciu è supporta nuove applicazioni fotoniche è MEMS. I wafer SiC di tipu P 4H/6H-P, drogati cù aluminiu à 1×10¹⁶–5×10¹⁸ cm⁻³, facilitanu architetture di dispositivi cumplementari.

I wafer PRIME di SiC sò sottumessi à una lucidatura chimica-meccanica à una rugosità superficiale RMS <0,2 nm, una variazione di spessore totale inferiore à 3 µm è una curvatura <10 µm. I substrati DUMMY acceleranu i testi di assemblaggio è di imballaggio, mentre chì i wafer RESEARCH presentanu spessori di epi-strati di 2-30 µm è un doping persunalizatu. Tutti i prudutti sò certificati da diffrazione di raggi X (curva di oscillazione <30 arcsec) è spettroscopia Raman, cù testi elettrici - misurazioni Hall, profilazione C-V è scansione di microtubi - chì garantiscenu a conformità JEDEC è SEMI.

E boule finu à 150 mm di diametru sò cultivate via PVT è CVD cù densità di dislocazioni inferiori à 1 × 10³ cm⁻² è un bassu numeru di micropipe. I cristalli di sementi sò tagliati à 0,1° da l'asse c per garantisce una crescita riproducibile è alte rese di taglio.

Cumbinendu parechji politipi, varianti di doping, gradi di qualità, dimensioni di wafer SiC è pruduzzione interna di boule è cristalli di semente, a nostra piattaforma di substrati SiC semplifica e catene di furnimentu è accelera u sviluppu di dispositivi per veiculi elettrici, reti intelligenti è applicazioni in ambienti difficili.

Scheda tecnica di u wafer SiC di tipu 4H-N da 6 pollici

| Scheda tecnica di wafer SiC da 6 pollici | ||||

| Parametru | Sottoparametru | Gradu Z | Gradu P | Gradu D |

| Diametru | 149,5–150,0 mm | 149,5–150,0 mm | 149,5–150,0 mm | |

| Spessore | 4H-N | 350 µm ± 15 µm | 350 µm ± 25 µm | 350 µm ± 25 µm |

| Spessore | 4H-SI | 500 µm ± 15 µm | 500 µm ± 25 µm | 500 µm ± 25 µm |

| Orientazione di a cialda | Fora d'asse: 4,0° versu <11-20> ±0,5° (4H-N); Nantu à l'asse: <0001> ±0,5° (4H-SI) | Fora d'asse: 4,0° versu <11-20> ±0,5° (4H-N); Nantu à l'asse: <0001> ±0,5° (4H-SI) | Fora d'asse: 4,0° versu <11-20> ±0,5° (4H-N); Nantu à l'asse: <0001> ±0,5° (4H-SI) | |

| Densità di i microtubi | 4H-N | ≤ 0,2 cm⁻² | ≤ 2 cm⁻² | ≤ 15 cm⁻² |

| Densità di i microtubi | 4H-SI | ≤ 1 cm⁻² | ≤ 5 cm⁻² | ≤ 15 cm⁻² |

| Resistività | 4H-N | 0,015–0,024 Ω·cm | 0,015–0,028 Ω·cm | 0,015–0,028 Ω·cm |

| Resistività | 4H-SI | ≥ 1×10¹⁰ Ω·cm | ≥ 1×10⁵ Ω·cm | |

| Orientazione Piatta Primaria | [10-10] ± 5,0° | [10-10] ± 5,0° | [10-10] ± 5,0° | |

| Lunghezza piatta primaria | 4H-N | 47,5 mm ± 2,0 mm | ||

| Lunghezza piatta primaria | 4H-SI | Tacca | ||

| Esclusione di u bordu | 3 mm | |||

| Orditura/LTV/TTV/Arcu | ≤2,5 µm / ≤6 µm / ≤25 µm / ≤35 µm | ≤5 µm / ≤15 µm / ≤40 µm / ≤60 µm | ||

| Rugosità | Pulaccu | Ra ≤ 1 nm | ||

| Rugosità | CMP | Ra ≤ 0,2 nm | Ra ≤ 0,5 nm | |

| Crepe di u bordu | Nimu | Lunghezza cumulativa ≤ 20 mm, singola ≤ 2 mm | ||

| Piatti esagonali | Area cumulativa ≤ 0,05% | Area cumulativa ≤ 0,1% | Area cumulativa ≤ 1% | |

| Zone di politipu | Nimu | Area cumulativa ≤ 3% | Area cumulativa ≤ 3% | |

| Inclusioni di carbone | Area cumulativa ≤ 0,05% | Area cumulativa ≤ 3% | ||

| Graffii di superficia | Nimu | Lunghezza cumulativa ≤ 1 × diametru di a cialda | ||

| Chips di bordu | Nisunu permessu ≥ 0,2 mm larghezza è prufundità | Finu à 7 chips, ≤ 1 mm ognunu | ||

| TSD (Dislocazione di a Vite di Filettatura) | ≤ 500 cm⁻² | N/D | ||

| BPD (Dislocazione di u Pianu di Base) | ≤ 1000 cm⁻² | N/D | ||

| Cuntaminazione di a superficia | Nimu | |||

| Imballaggio | Cassetta multi-wafer o contenitore di wafer unicu | Cassetta multi-wafer o contenitore di wafer unicu | Cassetta multi-wafer o contenitore di wafer unicu | |

Scheda tecnica di u wafer SiC di tipu 4H-N di 4 pollici

| Scheda tecnica di u wafer di SiC di 4 pollici | |||

| Parametru | Pruduzzione Zero MPD | Gradu di Pruduzzione Standard (Gradu P) | Gradu fittiziu (Gradu D) |

| Diametru | 99,5 mm–100,0 mm | ||

| Spessore (4H-N) | 350 µm ± 15 µm | 350 µm ± 25 µm | |

| Spessore (4H-Si) | 500 µm ± 15 µm | 500 µm ± 25 µm | |

| Orientazione di a cialda | Fora d'asse: 4,0° versu <1120> ±0,5° per 4H-N; Nantu à l'asse: <0001> ±0,5° per 4H-Si | ||

| Densità di Micropipe (4H-N) | ≤0,2 cm⁻² | ≤2 cm⁻² | ≤15 cm⁻² |

| Densità di Micropipe (4H-Si) | ≤1 cm⁻² | ≤5 cm⁻² | ≤15 cm⁻² |

| Resistività (4H-N) | 0,015–0,024 Ω·cm | 0,015–0,028 Ω·cm | |

| Resistività (4H-Si) | ≥1E10 Ω·cm | ≥1E5 Ω·cm | |

| Orientazione Piatta Primaria | [10-10] ±5,0° | ||

| Lunghezza piatta primaria | 32,5 mm ±2,0 mm | ||

| Lunghezza piatta secundaria | 18,0 mm ±2,0 mm | ||

| Orientazione Piatta Secundaria | Faccia di silicone in sù: 90° in sensu orariu da u pianu principale ±5,0° | ||

| Esclusione di u bordu | 3 mm | ||

| LTV/TTV/Deformazione d'arcu | ≤2,5 µm/≤5 µm/≤15 µm/≤30 µm | ≤10 µm/≤15 µm/≤25 µm/≤40 µm | |

| Rugosità | Ra di lucidatura ≤1 nm; CMP Ra ≤0,2 nm | Ra ≤0,5 nm | |

| Crepe di bordu da luce d'alta intensità | Nimu | Nimu | Lunghezza cumulativa ≤10 mm; lunghezza unica ≤2 mm |

| Piatti esagonali da luce d'alta intensità | Area cumulativa ≤0,05% | Area cumulativa ≤0,05% | Area cumulativa ≤0,1% |

| Zone Politipiche per Luce d'Alta Intensità | Nimu | Area cumulativa ≤3% | |

| Inclusioni di Carboniu Visuale | Area cumulativa ≤0,05% | Area cumulativa ≤3% | |

| Graffii di a superficia di u silicone da a luce d'alta intensità | Nimu | Lunghezza cumulativa ≤1 diametru di a cialda | |

| Chip di bordu da luce d'alta intensità | Nisunu permessu ≥0,2 mm di larghezza è prufundità | 5 permessi, ≤1 mm ognunu | |

| Cuntaminazione di a superficia di u siliciu da a luce d'alta intensità | Nimu | ||

| Dislocazione di a vite di filettatura | ≤500 cm⁻² | N/D | |

| Imballaggio | Cassetta multi-wafer o contenitore di wafer unicu | Cassetta multi-wafer o contenitore di wafer unicu | Cassetta multi-wafer o contenitore di wafer unicu |

Scheda tecnica di u wafer SiC di tipu HPSI di 4 pollici

| Scheda tecnica di u wafer SiC di tipu HPSI di 4 pollici | |||

| Parametru | Gradu di pruduzzione Zero MPD (Gradu Z) | Gradu di Pruduzzione Standard (Gradu P) | Gradu fittiziu (Gradu D) |

| Diametru | 99,5–100,0 mm | ||

| Spessore (4H-Si) | 500 µm ±20 µm | 500 µm ±25 µm | |

| Orientazione di a cialda | Fora d'asse: 4,0° versu <11-20> ±0,5° per 4H-N; Nantu à l'asse: <0001> ±0,5° per 4H-Si | ||

| Densità di Micropipe (4H-Si) | ≤1 cm⁻² | ≤5 cm⁻² | ≤15 cm⁻² |

| Resistività (4H-Si) | ≥1E9 Ω·cm | ≥1E5 Ω·cm | |

| Orientazione Piatta Primaria | (10-10) ±5,0° | ||

| Lunghezza piatta primaria | 32,5 mm ±2,0 mm | ||

| Lunghezza piatta secundaria | 18,0 mm ±2,0 mm | ||

| Orientazione Piatta Secundaria | Faccia di silicone in sù: 90° in sensu orariu da u pianu principale ±5,0° | ||

| Esclusione di u bordu | 3 mm | ||

| LTV/TTV/Deformazione d'arcu | ≤3 µm/≤5 µm/≤15 µm/≤30 µm | ≤10 µm/≤15 µm/≤25 µm/≤40 µm | |

| Rugosità (faccia C) | Pulaccu | Ra ≤1 nm | |

| Rugosità (faccia Si) | CMP | Ra ≤0,2 nm | Ra ≤0,5 nm |

| Crepe di bordu da luce d'alta intensità | Nimu | Lunghezza cumulativa ≤10 mm; lunghezza unica ≤2 mm | |

| Piatti esagonali da luce d'alta intensità | Area cumulativa ≤0,05% | Area cumulativa ≤0,05% | Area cumulativa ≤0,1% |

| Zone Politipiche per Luce d'Alta Intensità | Nimu | Area cumulativa ≤3% | |

| Inclusioni di Carboniu Visuale | Area cumulativa ≤0,05% | Area cumulativa ≤3% | |

| Graffii di a superficia di u silicone da a luce d'alta intensità | Nimu | Lunghezza cumulativa ≤1 diametru di a cialda | |

| Chip di bordu da luce d'alta intensità | Nisunu permessu ≥0,2 mm di larghezza è prufundità | 5 permessi, ≤1 mm ognunu | |

| Cuntaminazione di a superficia di u siliciu da a luce d'alta intensità | Nimu | Nimu | |

| Dislocazione di a vite di filettatura | ≤500 cm⁻² | N/D | |

| Imballaggio | Cassetta multi-wafer o contenitore di wafer unicu | ||

Applicazione di e cialde di SiC

-

Moduli di alimentazione a wafer SiC per inverter EV

I MOSFET è i diodi basati nantu à wafer di SiC custruiti nantu à substrati di wafer di SiC di alta qualità offrenu perdite di commutazione ultra basse. Sfruttendu a tecnulugia di i wafer di SiC, sti moduli di putenza operanu à tensioni è temperature più elevate, permettendu inverter di trazione più efficienti. L'integrazione di i die di wafer di SiC in i stadi di putenza riduce i requisiti di raffreddamentu è l'ingombro, mettendu in mostra tuttu u putenziale di l'innuvazione di i wafer di SiC. -

Dispositivi RF è 5G à alta frequenza nantu à wafer SiC

L'amplificatori è l'interruttori RF fabbricati nantu à piattaforme di wafer SiC semi-isolanti mostranu una cunduttività termica è una tensione di rottura superiori. U substratu di u wafer SiC minimizza e perdite dielettriche à e frequenze GHz, mentre chì a resistenza di u materiale di u wafer SiC permette un funziunamentu stabile in cundizioni di alta putenza è alta temperatura, ciò chì face di u wafer SiC u substratu di scelta per e stazioni base 5G di prossima generazione è i sistemi radar. -

Substrati Optoelettronici è LED da Wafer SiC

I LED blu è UV cresciuti nantu à substrati di wafer di SiC beneficianu di una eccellente corrispondenza di reticolo è dissipazione di u calore. L'usu di un wafer di SiC lucidatu à faccia C assicura strati epitassiali uniformi, mentre chì a durezza inerente di u wafer di SiC permette un assottigliamento fine di u wafer è un imballaggio affidabile di u dispositivu. Questu face di u wafer di SiC a piattaforma di riferimentu per l'applicazioni LED di alta putenza è longa durata.

Dumande è risposte nantu à e cialde di SiC

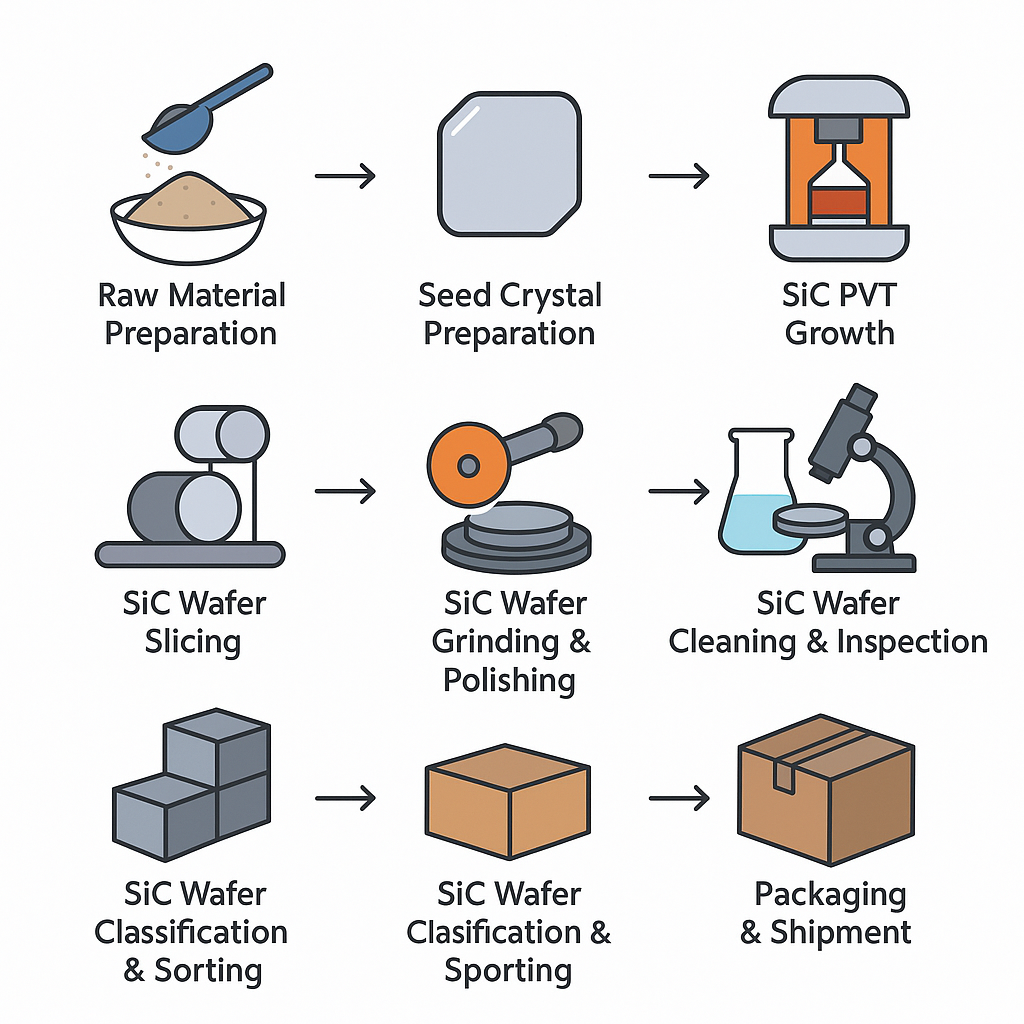

1. D: Cumu sò fabbricati i wafer di SiC?

A:

Wafer di SiC fabbricatiPassi dettagliati

-

Cialde di SiCPreparazione di materie prime

- Aduprà polvere di SiC di qualità ≥5N (impurità ≤1 ppm).

- Setacciate è precotte per rimuovere i cumposti residuali di carbone o azotu.

-

SiCPreparazione di Cristalli di Seme

-

Pigliate un pezzu di cristallu unicu 4H-SiC, tagliatelu longu l'orientazione 〈0001〉 à ~10 × 10 mm².

-

Lucidatura di precisione à Ra ≤0.1 nm è marcatura di l'orientazione di u cristallu.

-

-

SiCCrescita PVT (Trasportu Fisicu di Vapore)

-

Caricate u crogiolu di grafite: in fondu cù polvere di SiC, in cima cù cristallu di sementi.

-

Evacuate à 10⁻³–10⁻⁵ Torr o riempite cù eliu d'alta purità à 1 atm.

-

Riscaldà a zona di a fonte à 2100–2300 ℃, mantene a zona di sementi 100–150 ℃ più fresca.

-

Cuntrullà u ritmu di crescita à 1–5 mm/h per equilibrà a qualità è u rendimentu.

-

-

SiCRicottura di lingotti

-

Ricottura u lingotto di SiC appena cresciutu à 1600–1800 ℃ per 4-8 ore.

-

Scopu: alleviare e tensioni termiche è riduce a densità di dislocazioni.

-

-

SiCAffettatura di cialde

-

Aduprate una sega à filu diamantatu per taglià u lingotto in cialde di 0,5-1 mm di spessore.

-

Minimizà e vibrazioni è a forza laterale per evità micro-fessure.

-

-

SiCCialdeaMolatura è lucidatura

-

Macinazione grossolanaper rimuovere i danni da segatura (rugosità ~10–30 µm).

-

Macinazione finaper ottene una planarità ≤5 µm.

-

Lucidatura Chimico-Meccanica (CMP)per ghjunghje à una finitura speculare (Ra ≤0,2 nm).

-

-

SiCCialdeaPulizia è Ispezione

-

Pulizia à ultrasoniin soluzione di Piranha (H₂SO₄:H₂O₂), acqua DI, poi IPA.

-

Spettroscopia XRD/Ramanper cunfirmà u politipu (4H, 6H, 3C).

-

Interferometriaper misurà a planarità (<5 µm) è a deformazione (<20 µm).

-

Sonda à quattru puntiper pruvà a resistività (per esempiu HPSI ≥10⁹ Ω·cm).

-

Ispezione di difettisottu à un microscopiu à luce polarizzata è à un tester di graffi.

-

-

SiCCialdeaClassificazione è Ordinamentu

-

Ordina i wafer per politipu è tipu elettricu:

-

4H-SiC tipu N (4H-N): cuncentrazione di purtatori 10¹⁶–10¹⁸ cm⁻³

-

4H-SiC Semi-isolante d'alta purezza (4H-HPSI): resistività ≥10⁹ Ω·cm

-

6H-SiC di tipu N (6H-N)

-

Altri: 3C-SiC, tipu P, ecc.

-

-

-

SiCCialdeaImballaggio è spedizione

2. D: Quali sò i principali vantaghji di e cialde di SiC rispetto à e cialde di siliciu?

A: In paragone cù i wafer di siliciu, i wafer di SiC permettenu:

-

Funzionamentu à tensione più alta(>1.200 V) cù una resistenza di attivazione più bassa.

-

Stabilità di temperatura più alta(>300 °C) è una migliore gestione termica.

-

Velocità di cummutazione più rapidecù perdite di commutazione più basse, riducendu u raffreddamentu à livellu di sistema è a dimensione in i convertitori di putenza.

4. D: Quali difetti cumuni affettanu u rendimentu è e prestazioni di e cialde di SiC?

A: I difetti primari in i wafer di SiC includenu micropipi, dislocazioni di u pianu basale (BPD) è graffi superficiali. I micropipi ponu causà guasti catastrofichi di u dispusitivu; i BPD aumentanu a resistenza à l'attivazione cù u tempu; è i graffi superficiali portanu à a rottura di u wafer o à una scarsa crescita epitassiale. L'ispezione rigorosa è a mitigazione di i difetti sò dunque essenziali per massimizà u rendimentu di u wafer di SiC.

Data di publicazione: 30 di ghjugnu di u 2025